- Table of Contents

-

- 15-Network Management and Monitoring Configuration Guide

- 00-Preface

- 01-System maintenance and debugging configuration

- 02-NQA configuration

- 03-iNQA configuration

- 04-iFIT configuration

- 05-SRPM configuration

- 06-NTP configuration

- 07-PTP configuration

- 08-Network synchronization configuration

- 09-SNMP configuration

- 10-RMON configuration

- 11-NETCONF configuration

- 12-CWMP configuration

- 13-EAA configuration

- 14-Process monitoring and maintenance configuration

- 15-Sampler configuration

- 16-Mirroring configuration

- 17-NetStream configuration

- 18-IPv6 NetStream configuration

- 19-TCP connection trace configuration

- 20-Performance management configuration

- 21-Fast log output configuration

- 22-Flow log configuration

- 23-Information center configuration

- 24-Packet capture configuration

- 25-Flow monitor configuration

- Related Documents

-

| Title | Size | Download |

|---|---|---|

| 08-Network synchronization configuration | 156.54 KB |

Configuring network synchronization

Network synchronization tasks at a glance

Configuring clock reference selection

Enabling automatic clock reference selection

Specifying a clock reference manually

Setting an Sa bit for the SSM of BITS clocks

Setting the frequency of a BITS clock

Configuring automatic reference selection parameters

Configuring the method for setting the SSM quality level of a clock source

Specifying an SSM quality level for a clock source

Controlling the use of SSM in automatic reference selection

Setting a priority for a clock source

Setting the SSM level degradation threshold for the clock reference

Configuring clock frequency deviation detection

Display and maintenance commands for network clock monitoring module

Network synchronization configuration examples

Example: Configuring network synchronization

Configuring synchronous Ethernet

System clock QL distribution and SyncE port input QL updating

Restrictions and guidelines: SyncE

Configuring SyncE on an Ethernet interface

Setting the clock mode on a copper SyncE GE port

Display and maintenance commands for SyncE

Synchronous Ethernet configuration examples

Configuring network synchronization

About network synchronization

The network clock monitoring module provides network clock synchronization for all interface cards in the system. It ensures that all ports on the interface cards operate at the same clock rates for network synchronization.

The network clock monitoring module provides the following functions:

· Provides highly precise, reliable timing signal to all interface cards.

· Constantly monitors the signaling status on the interface cards.

· Selects a clock reference from available clock sources, and then distributes its timing signal to all interface cards.

· Performs phase lock to maintain a deterministic relationship between the input and output signals in frequency and phase.

Clock sources

A clock source provides timing signals for the device. Clock sources are classified into the following four types in descending order of precision.

· BITS—Building integrated timing supply (BITS) clock. The MPU has BITS ports to receive and send timing signals.

· PTP—Timing signal obtained through PTP.

· Line clock—Timing signal extracted from the signal received on a port from a higher-level device. The port is called a line processing unit (LPU) port.

· Local clock source—38.88 MHz timing signal generated by a crystal oscillator on the clock daughter card. The local clock signal has the lowest precision.

Clock source attributes

When the device receives timing signals from multiple clock sources, it will select an optimal one from the clock sources as its reference clock (reference source). In automatic clock reference selection, the clock reference is selected based on the SSM quality level and priority.

SSM quality levels

The synchronization status message (SSM) is transmitted in a synchronization distribution trail to indicate the quality of the clock source. The following are the SSM quality levels supported by the device, from the highest to the lowest:

· PRC—G.811 primary reference clock.

· SSU-A—G.812 primary-level SSU.

· SSU-B—G.812 second-level SSU.

· SEC—SDH equipment clock.

· Unknown—Synchronization quality unknown.

· DNU—Do not use for synchronization.

Priority

For a clock source to be selected as the clock reference, assign it a lower priority value than other clock sources. The lower the priority value, the better the clock source. For example, the clock source with a priority of 1 is better than the clock source with a priority of 3.

Clock reference selection

The network clock monitoring module supports automatic and manual clock reference selection.

Automatic reference selection

In an automatic reference selection process, the network clock monitoring module uses the SSM quality level, clock source priority, and clock source number to make a selection decision. The use of SSM in the automatic reference selection process is user configurable.

The selection process is as follows:

1. If SSM is enabled for automatic reference selection, the module selects the clock source with the highest SSM quality level.

2. If SSM is disabled for automatic reference selection, or clock sources have the same SSM quality level, the module selects the clock source with the lowest priority value. (A lower priority value indicates a better clock source.)

3. If the clock sources have the same priority, the module selects the clock source that has the lowest slot-number/subslot-number/port-number sequence.

After selecting the best reference, the network clock monitoring module distributes the selected timing signal to all interface cards, and locks the timing to the reference signal. When the traced timing signal is lost, the network clock monitoring module selects the next optimal clock reference. When the signal of the best clock source can be traced again, the module selects the best clock source to replace the less optimal clock source as the reference.

|

|

NOTE: A clock source will not compete in automatic reference selection if the clock source is in one of the following conditions: · The timing signal cannot be detected. · The clock source priority is 255. · The SSM quality level is DNU. |

Manual reference selection

In manual reference selection mode, you specify a clock source as the reference. If the specified clock reference is invalid, the module uses the local clock timing signal. After using the specified clock reference, the network clock monitoring module does not change the clock reference automatically. When the signal of the specified clock reference is lost, the module changes to the holdover state. In this state, the module continues to distribute the signal of the clock reference to the interface cards.

Clock mode on a port

|

IMPORTANT: Set the clock mode to slave on the port connected to a SONET/SDH device, because the SONET/SDH clock is more precise. |

A port can operate in one of the following clock modes:

· Master—The port provides timing to the peer end. The timing signal is derived from the network clock monitoring module.

¡ If automatic reference selection is used, the timing signal is derived from the reference clock selected by the network clock monitoring module.

¡ If manual reference selection is used, the timing signal is derived from the manually specified clock reference.

¡ If the manually specified clock reference is not available, the port outputs the timing signal generated by the local clock.

· Slave—The port uses the timing signal received from the peer end. For the network clock monitoring module to extract timing signal from a port, you must place the port in slave clock mode. If the port is in master clock mode, the module does not extract the timing signal from the incoming traffic on the port.

Network synchronization tasks at a glance

To configure network synchronization, perform the following tasks:

1. Configuring clock reference selection

¡ Enabling automatic clock reference selection

¡ Specifying a clock reference manually

2. (Optional.) Configuring BITS clocks

a. Setting an Sa bit for the SSM of BITS clocks

b. Setting the frequency of a BITS clock

3. (Optional.) Specifying a line clock

4. (Optional.) Configuring automatic reference selection parameters

¡ Configuring the method for setting the SSM quality level of a clock source

¡ Specifying an SSM quality level for a clock source

¡ Controlling the use of SSM in automatic reference selection

¡ Setting a priority for a clock source

Configuring clock reference selection

Enabling automatic clock reference selection

1. Enter system view.

system-view

2. Enable automatic clock reference selection

In standalone mode:

network-clock work-mode auto

In IRF mode:

network-clock chassis chassis-number work-mode auto

By default, clock reference is selected automatically.

Specifying a clock reference manually

Restrictions and guidelines

To use the timing signal from an interface as the synchronization reference, you must also specify the interface as a line clock input port by using the network-clock lpuport command.

If manual reference selection is used, the SSM levels and priorities configured for the clock sources do not take effect.

Procedure

1. Enter system view.

system-view

2. Specify a clock reference manually.

In standalone mode:

network-clock work-mode manual source { bits0 | bits1 | lpuport interface-type interface-number | ptp }

In IRF mode:

network-clock chassis chassis-number work-mode manual source { bits0 | bits1 | ptp }

network-clock work-mode manual source lpuport interface-type interface-number

By default, the clock reference is selected automatically.

Configuring BITS clocks

Setting an Sa bit for the SSM of BITS clocks

About this task

Sa bits from Sa4 through Sa8 can be used to transmit the SSM quality level of BITS timing signal. Select one Sa bit as required by the network.

Restrictions and guidelines

Procedure

1. Enter system view.

system-view

2. Specify an Sa bit for the SSM of a BITS clock.

In standalone mode:

network-clock source { bits0 | bits1 } sa-bit { sa4 | sa5 | sa6 | sa7 | sa8 }

In IRF mode:

network-clock chassis chassis-number source { bits0 | bits1 } sa-bit { sa4 | sa5 | sa6 | sa7 | sa8 }

Setting the frequency of a BITS clock

About this task

You can set the frequency of a BITS clock to 2 Mbps or 2 MHz.

Procedure

1. Enter system view.

system-view

2. Set the frequency of a BITS clock.

In standalone mode:

network-clock source { bits0 | bits1 } frequency { bps-2m | hz-2m }

In IRF mode:

network-clock chassis chassis-number source { bits0 | bits1 } frequency { bps-2m | hz-2m }

By default, the frequency of a BITS clock is 2 Mbps.

Specifying a line clock

Restrictions and guidelines

Only main ports can be specified as line clock input ports. For the timing signal received on the line clock input port to be used for synchronization, you must set the port to operate in slave mode.

Procedure

1. Enter system view.

system view

2. Enter interface view.

interface interface-type interface-number

3. Specify the port as a line clock input port.

network-clock lpuport interface-type interface-number

By default, no line clock input port is configured.

Configuring automatic reference selection parameters

Configuring the method for setting the SSM quality level of a clock source

About this task

The network clock monitoring module can use one of the following methods to assign an SSM quality level to the timing signal from a clock source:

· Uses the SSM quality level extracted from the received timing signal.

· Uses the SSM quality level manually assigned as described in "Specifying an SSM quality level for a clock source."

Procedure

1. Enter system view.

system-view

2. Configure the method for setting the SSM quality level of a clock source.

In standalone mode:

network-clock source { bits0 | bits1 | lpuport interface-type interface-number | ptp } forcessm { off | on }

In IRF mode:

network-clock chassis chassis-number source { bits0 | bits1 | ptp } forcessm { off | on }

network-clock source lpuport interface-type interface-number forcessm { off | on }

By default, the quality level of a clock source is a user-defined value. The network clock monitoring module does not extract the quality level from the SSM sent by the clock source.

To extract the SSM quality level from the received timing signal, specify the off keyword. To use the manually assigned SSM quality level, specify the on keyword.

Specifying an SSM quality level for a clock source

Restrictions and guidelines

The SSM quality level you specify for a clock source takes effect only when manual SSM quality level assignment is enabled.

Procedure

1. Enter system view.

system-view

2. Assign an SSM quality level to a clock source.

In standalone mode:

network-clock source { bits0 | bits1 | lpuport interface-type interface-number | ptp } ssm { dnu | prc | sec | ssua | ssub | unknown }

In IRF mode:

network-clock chassis chassis-number source { bits0 | bits1 | ptp } ssm { dnu | prc | sec | ssua | ssub | unknown }

network-clock source lpuport interface-type interface-number ssm { dnu | prc | sec | ssua | ssub | unknown }

By default, all clock sources use the unknown SSM quality level.

DNU clock sources are excluded from automatic reference selection.

3. (Optional.) Verify that the configuration is effective.

display network-clock source

It takes time for the SSM quality level change to take effect. To verify the effectiveness of the change, you can also check the logs.

Controlling the use of SSM in automatic reference selection

Procedure

1. Enter system view.

system-view

2. Configure the use of SSM quality level in automatic reference selection.

In standalone mode:

network-clock ssmcontrol { off | on }

In IRF mode:

network-clock chassis chassis-number ssmcontrol { off | on }

By default, the SSM quality level is ignored in automatic reference selection.

To ignore the SSM quality level in clock reference selection, specify the off keyword. To use the SSM quality level in clock reference selection, specify the on keyword.

Setting a priority for a clock source

About this task

In an automatic reference selection process, the network clock monitoring module selects the optimal clock as a reference from all available clock sources.

Restrictions and guidelines

The lower the priority value, the higher the priority of the clock source. A clock source with a priority value of 255 will not take part in automatic reference selection.

Procedure

1. Enter system view.

system-view

2. Set a priority for a clock source.

In standalone mode:

network-clock source { bits0 | bits1 | lpuport interface-type interface-number | ptp } priority priority

In IRF mode:

network-clock chassis chassis-number source { bits0 | bits1 | ptp } priority priority

network-clock souce lpuport interface-type interface-number priority priority

By default, all clock sources have a priority of 255. None of the clock sources can be used in automatic clock reference selection.

Setting the SSM level degradation threshold for the clock reference

1. Enter system view.

system view

2. Set the SSM level degradation threshold for the clock reference.

In standalone mode:

network-clock ssm-degrade-threshold { dnu | prc | sec | ssua | ssub }

In IRF mode:

network-clock chassis chassis-number ssm-degrade-threshold { dnu | prc | sec | ssua | ssub }

By default, the SSM level degradation threshold is dnu.

Configuring clock frequency deviation detection

About this task

After clock frequency deviation detection is enabled, if the frequency difference between the signal of a clock source received on the device and the current clock reference exceeds the threshold, the system sets the frequency deviation status of the clock source to Abnormal. By default, clock sources in abnormal frequency difference status can compete in clock reference selection. As a best practice, disable clock sources in abnormal frequency difference status from competing in clock reference selection to ensure clock precision.

When the frequency deviation of a clock falls from abnormal status into the acceptable range, its frequency deviation status cannot change to normal automatically. You can use the network-clock freq-deviation-source elect recover command to change the frequency deviation status of the clock signal to normal manually so that it can compete in the clock reference election.

Procedure

1. Enter system view.

system view

2. Enable clock frequency deviation detection.

In standalone mode:

network-clock freq-deviation-detect enable

In IRF mode:

network-clock chassis chassis-number freq-deviation-detect enable

By default, clock frequency deviation detection is disabled.

3. Set a clock frequency deviation threshold.

In standalone mode:

network-clock freq-deviation-threshold offset-value

In IRF mode:

network-clock chassis chassis-number freq-deviation-threshold offset-value

By default, the clock frequency deviation threshold is 4600 ppb.

4. Disable clocks with abnormal frequency deviation status from competing in clock reference election.

In standalone mode:

network-clock freq-deviation-source elect disable

In IRF mode:

network-clock chassis chassis-number freq-deviation-source elect disable

By default, clocks with abnormal frequency deviation status are allowed to compete in clock reference election.

5. Enter interface view.

interface interface-type interface-number

6. Change the frequency deviation status of a clock signal to normal so that it can compete in the clock reference election.

network-clock freq-deviation-source elect recover

Display and maintenance commands for network clock monitoring module

Execute display commands in any view.

|

Task |

Command |

|

Display the frequency deviation status of clock signals received by the device. |

display network-clock freq-deviation status |

|

Display information about clock frequency deviation detection. |

In standalone mode: display network-clock freq-deviation-detect In IRF mode: display network-clock freq-deviation-detect [ chassis chassis-number ] |

|

Display the self-test result of the network clock monitoring module. |

In standalone mode: display network-clock self-test-result In IRF mode: display network-clock self-test-result [ chassis chassis-number ] |

|

Display information about the clock sources. |

In standalone mode: display network-clock source In IRF mode: display network-clock source [ chassis chassis-number ] |

|

Display the operating state of the network clock monitoring module. |

In standalone mode: display network-clock status In IRF mode: display network-clock status [ chassis chassis-number ] |

|

Display version information about the network clock monitoring module. |

In standalone mode: display network-clock version In IRF mode: display network-clock version [ chassis chassis-number ] |

|

Reset the clock state of the device. |

In standalone mode: reset network-clock In IRF mode: reset network-clock [ chassis chassis-number ] |

Network synchronization configuration examples

Example: Configuring network synchronization

Network configuration

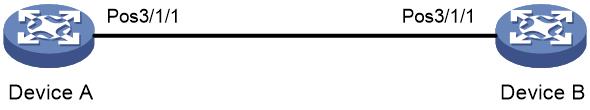

As shown in Figure 1, Device A obtains its timing signal from an external BITS clock.

Device A and Device B are connected on POS interfaces. Configure Device B to derive its timing from Device A through Pos 3/1/1.

Procedure

1. On Device A:

# Specify the master clock mode on Pos 3/1/1.

<DeviceA> system-view

[DeviceA] interface pos 3/1/1

[DeviceA-Pos3/1/1] clock master

[DeviceA-Pos3/1/1] quit

2. On Device B:

# Specify Pos 3/1/1 as a line clock input port.

<DeviceB> system-view

[DeviceB] network-clock lpuport pos 3/1/1

# Specify the slave clock mode on the Pos 3/1/1.

[DeviceB] interface pos 3/1/1

[DeviceB-Pos3/1/1] clock slave

[DeviceB-Pos3/1/1] quit

# Specify Pos 3/1/1 as the source to provide clock reference.

[DeviceB] network-clock work-mode manual source lpuport pos 3/1/1

[DeviceB] quit

Verifying the configuration

# Verify that Pos 3/1/1 provides the network clock reference for Device B.

<DeviceB> display network-clock status

Mode : Manual

Reference : pos 3/1/1

Traced reference : pos 3/1/1

Lock mode : Locked

OSC state : Normal

SSM output level : SSUB

SSM control enable: Off

Configuring synchronous Ethernet

About synchronous Ethernet

Synchronous Ethernet (SyncE) provides high-quality frequency synchronization on Ethernet at the physical layer. It can provide the same level of clock precision as SONET/SDH.

Transferring frequency signals at the physical layer, SyncE functions regardless of the network conditions such as congestion, packet loss, and delay.

Quality levels of clocks

SyncE devices use an Ethernet synchronization messaging channel (ESMC) to transmit the quality level (QL) of their system clocks. A SyncE device uses QL information to select the optimal clock reference from all available timing sources for its system clock.

The following are the QLs supported by the device, from the highest to the lowest:

· PRC—G.811 primary reference clock.

· SSU-A—G.812 primary-level SSU.

· SSU-B—G.812 second-level SSU.

· SEC—SDH equipment clock.

· DNU—Do not use for synchronization.

· UNK—Synchronization quality unknown.

DNU clock sources cannot participate in clock reference selection.

Clock reference selection

The system clock uses the clock reference selected with the highest QL from the following sources. If these sources have the same QL, the system clock selects the clock reference by priority, from the highest to the lowest:

· External clock sources.

· Line clock sources input from interfaces.

· Internal clock sources.

The system clock uses the QL of the selected reference. Clock reference selection process starts each time the QL of a source is updated.

|

|

NOTE: If QLs are the same on two interfaces, the clock source input from the lower-numbered interface has priority. |

System clock QL distribution and SyncE port input QL updating

Distribution of the system clock QL

When distributing the QL of the system clock, the system uses the following rules:

· If the clock reference is not from a SyncE port, the system distributes the QL out of all SyncE ports.

· If the clock reference is from a SyncE port, the system distributes the QL out of all SyncE ports except for the reference input port. To prevent timing loops, the sent QL is DNU on the timing reference input port.

Input QL updating on SyncE ports

The default input QL is Unknown on a SyncE port. A SyncE port with an input QL of Unknown cannot be used as a line clock input port. The port updates its input QL when it receives a quality level higher than Unknown. The Unknown level will be restored if the port does not receive ESMC packets within 5 seconds after the update.

Protocols and standards

· ITU-T G.781, Synchronization Layer Functions

· ITU-T G.813, Timing characteristics of SDH equipment slave clocks (SEC)

· ITU-T G.823, The control of jitter and wander within digital networks which are based on the 2048 kbit/s hierarchy

· ITU-T G.8261, Timing and Synchronization Aspects in Packet Networks

· ITU-T G.8262, Timing Characteristics of a Synchronous Ethernet Equipment Slave Clock (EEC)

· ITU-T G.8264/Y.1364, Distribution of Timing Information through Packet Networks

Restrictions and guidelines: SyncE

A subcard interface operating in WAN mode does not support SyncE. For more information about WAN mode, see Ethernet interface configuration in Interface Configuration Guide.

Only these interfaces on the following subcards and cards support SyncE:

· 1000 Mbps optical interfaces on the following subcards:

¡ NIC-GP24L1

¡ NIC-GP24L1A

¡ MIC-GP10L-V2

¡ MIC-GP20L

· 10 Gbps interfaces on the following subcards:

¡ RX-NIC-XP5L

¡ RX-NIC-XP10L

¡ RX-NIC-XP20L

¡ NIC-XP5L

¡ NIC-XP10L

¡ NIC-XP20L

· 10 Gbps interfaces operating in LAN mode on the following subcards:

¡ NIC-XP20L1

· 10 Gbps and 25 Gbps interfaces on the following subcards:

¡ RX-NIC-YGS4L

· 50 Gbps interfaces on the following subcards:

¡ RX-NIC-LGQ2L

¡ RX-NIC-LGQ4L

¡ NIC-LGQ2L

¡ NIC-LGQ4L

· 100 Gbps interfaces on the following subcards:

¡ RX-NIC-CC1L

¡ RX-NIC-CC2L

¡ RX-NIC-CQ1LF

¡ RX-NIC-CQ2LF

¡ NIC-CC1L

¡ NIC-CC2L

¡ NIC-CQ1L

¡ NIC-CQ2L

· 10 Gbps interfaces on the CEPC-XP48RX card

· 10 Gbps operating in LAN mode on the CEPC-XP24LX card

· 1000 Mbps interfaces on the following subcards:

¡ MIC-GT20L

· 10 Gbps interfaces operating in LAN mode on the following subcards:

¡ MIC-XP2L

¡ MIC-XP2L-LAN

¡ MIC-XP4L1

¡ MIC-XP5L

¡ MIC-XP5L1

¡ MIC-XP8L

¡ MIC-XP20L

For information about LAN/WAN switching, see Ethernet interface configuration in Interface Configuration Guide.

· 100 Gbps interfaces on the following subcards:

¡ MIC-CQ2L

¡ MIC-CP1L

¡ MIC-CQ1L1

· Interfaces on the following cards:

¡ CSPEX-1304X

¡ CSPEX-1404X

¡ CSPEX-1502X

¡ CSPEX-1504X

¡ CSPEX-1504XA

¡ CSPEX-1602X

¡ CSPEX-1602XA

¡ CSPEX-1512X

¡ CSPEX-1612X

¡ CSPEX-1812X

¡ RX-SPE200

¡ CEPC-XP4LX

¡ CEPC-XP24LX

¡ CEPC-XP48RX

¡ CEPC-CP4RX

¡ CEPC-CP4RXA

¡ CEPC-CP4RX-L

¡ CSPEX-1802X

¡ CSPEX-1802XA

¡ CSPEX-1812X-E

¡ CSPEX-2304X-G

¡ CEPC-CQ8L

¡ CEPC-CQ8LA

¡ CEPC-CQ16L1

¡ CSPEX-1502XA

¡ RX-SPE200-E

For SyncE to function correctly, make sure the device is installed with the CSR05SRP1L3, CSR05SRP1R3, CSR05SRP1P3, or CSR05SRP1P3-G MPU.

SyncE is not supported when the device operates in IRF mode. For information about IRF, see IRF configuration in Virtual Technologies Configuration Guide.

For an MIC-GT20L subcard interface to derive timing from an upstream clock, you must configure the synce state slave command on the interface.

Configuring SyncE on an Ethernet interface

1. Enter system view.

system-view

2. Enter Ethernet interface view or FlexE physical interface view.

interface interface-type interface-number

3. Enable the synchronous mode.

synchronous mode

By default, Ethernet interfaces are in the non-synchronous mode. An interface can participate in the clock reference selection only when it is in the synchronous mode.

4. (Optional.) Assign the interface to an ESMC bundle.

esmc bundle bundle-number

By default, an interface is not assigned to an ESMC bundle.

5. Enable ESMC to transmit QL information.

esmc enable

By default, ESMC is disabled on Ethernet interfaces.

Setting the clock mode on a copper SyncE GE port

About this task

Configure the clock mode for a copper SyncE GE port based on its time synchronization direction.

Restrictions and guidelines

By default, a copper SyncE GE port automatically negotiates its clock mode with the remote end. To avoid a negotiation result that conflicts with your clock synchronization trail design, manually set the clock mode.

· To derive timing from the upstream clock, set the clock mode to slave.

· To provide timing for the downstream clock, set the clock mode to master.

Procedure

1. Enter system view.

system-view

2. Enter Ethernet interface view.

interface interface-type interface-number

3. Set the clock mode.

synce state { master | slave }

By default, the clock mode of a copper SyncE GE port is automatically negotiated.

Display and maintenance commands for SyncE

Execute display commands in any view.

|

Task |

Command |

|

Display ESMC information. |

display esmc [ interface interface-type interface-number ] |

Synchronous Ethernet configuration examples

Example: Configuring SyncE

Network configuration

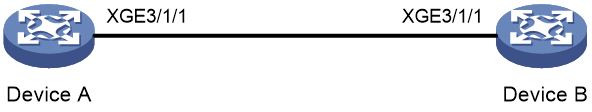

As shown in Figure 2, configure SyncE on the devices for high-precision frequency synchronization.

Procedure

# On Device A, enable the synchronous mode and ESMC on Ten-GigabitEthernet 3/1/1.

<DeviceA> system-view

[DeviceA] interface ten-gigabitethernet 3/1/1

[DeviceA-Ten-GigabitEthernet3/1/1] synchronous mode

[DeviceA-Ten-GigabitEthernet3/1/1] esmc enable

[DeviceA-Ten-GigabitEthernet3/1/1] quit

# On Device B, enable the synchronous mode and ESMC on Ten-GigabitEthernet 3/1/1.

<DeviceB> system-view

[DeviceB] interface ten-gigabitethernet 3/1/1

[DeviceB-Ten-GigabitEthernet3/1/1] synchronous mode

[DeviceB-Ten-GigabitEthernet3/1/1] esmc enable

[DeviceB-Ten-GigabitEthernet3/1/1] quit

Verifying the configuration

# Verify that ESMC is enabled on both Device A and Device B when they are connected to their respective clock references. The clock QLs of Device A and Device B are QL-PRC and QL-SEC, respectively. Device A provides more precise timing than Device B.

[DeviceA] display esmc

Interface : Ten-GigabitEthernet3/1/1

Mode : Synchronous

ESMC status : Enable

ESMC bundle : N/A

Port status : Up

Duplex mode : Full

QL received : QL-SEC

QL sent : QL-PRC

ESMC information packets received : 2195

ESMC information packets sent : 6034

ESMC event packets received : 1

ESMC event packets sent : 1

ESMC information rate : 1 packets/sec

ESMC expiration : 5 seconds

[DeviceB] display esmc

Interface : Ten-GigabitEthernet3/1/1

Mode : Synchronous

ESMC status : Enable

ESMC bundle : N/A

Port status : Up

Duplex mode : Full

QL received : QL-PRC

QL sent : QL-SEC

ESMC information packets received : 6034

ESMC information packets sent : 2195

ESMC event packets received : 1

ESMC event packets sent : 1

ESMC information rate : 1 packets/sec

ESMC expiration : 5 seconds

# Verify that QL information is exchanged correctly after synchronization between Device A and Device B. Ten-GigabitEthernet3/1/1 on Device B becomes a reference input port. The clock QL sent from Device B to Device A changes to QL-DNU.

[DeviceA] display esmc

Interface : Ten-GigabitEthernet3/1/1

Mode : Synchronous

ESMC status : Enable

ESMC bundle : N/A

Port status : Up

Duplex mode : Full

QL received : QL-DNU

QL sent : QL-PRC

ESMC information packets received : 2573

ESMC information packets sent : 6412

ESMC event packets received : 1

ESMC event packets sent : 1

ESMC information rate : 1 packets/sec

ESMC expiration : 5 seconds

[DeviceB] display esmc

Interface : Ten-GigabitEthernet3/1/1

Mode : Synchronous

ESMC status : Enable

ESMC bundle : N/A

Port status : Up

Duplex mode : Full

QL received : QL-PRC

QL sent : QL-DNU

ESMC information packets received : 6412

ESMC information packets sent : 2573

ESMC event packets received : 1

ESMC event packets sent : 1

ESMC information rate : 1 packets/sec

ESMC expiration : 5 seconds